韩国媒体报道,尽管三星正在加大3nm芯片的研发力度,但由于工艺技术还不够成熟,良率仅达到60%,这意味着每生产出一颗3nm芯片,就需要投入更多的人力和资源进行调试。这对于全球半导体产业来说是一个巨大的挑战。

据韩国媒体DealSite报道,三星电子3nm制程良率堪忧,目前仍徘徊在50%左右,尚未达到60%。

自2022年6月三星宣布量产3nm技术以来,关于其良品率的报道不一。2023年5月,三星宣称其3nm的良率可以达到60~70%。7月,Hi Investment & Securities还声称其3nm的收益率达到60%,但在10月,另一家韩国媒体Chosunbiz声称其3nm的收益率只有50%左右,并在今年1月补充。

三星3nm良率低的主要问题是其GAA工艺还不够稳定,直接影响良率的提升。

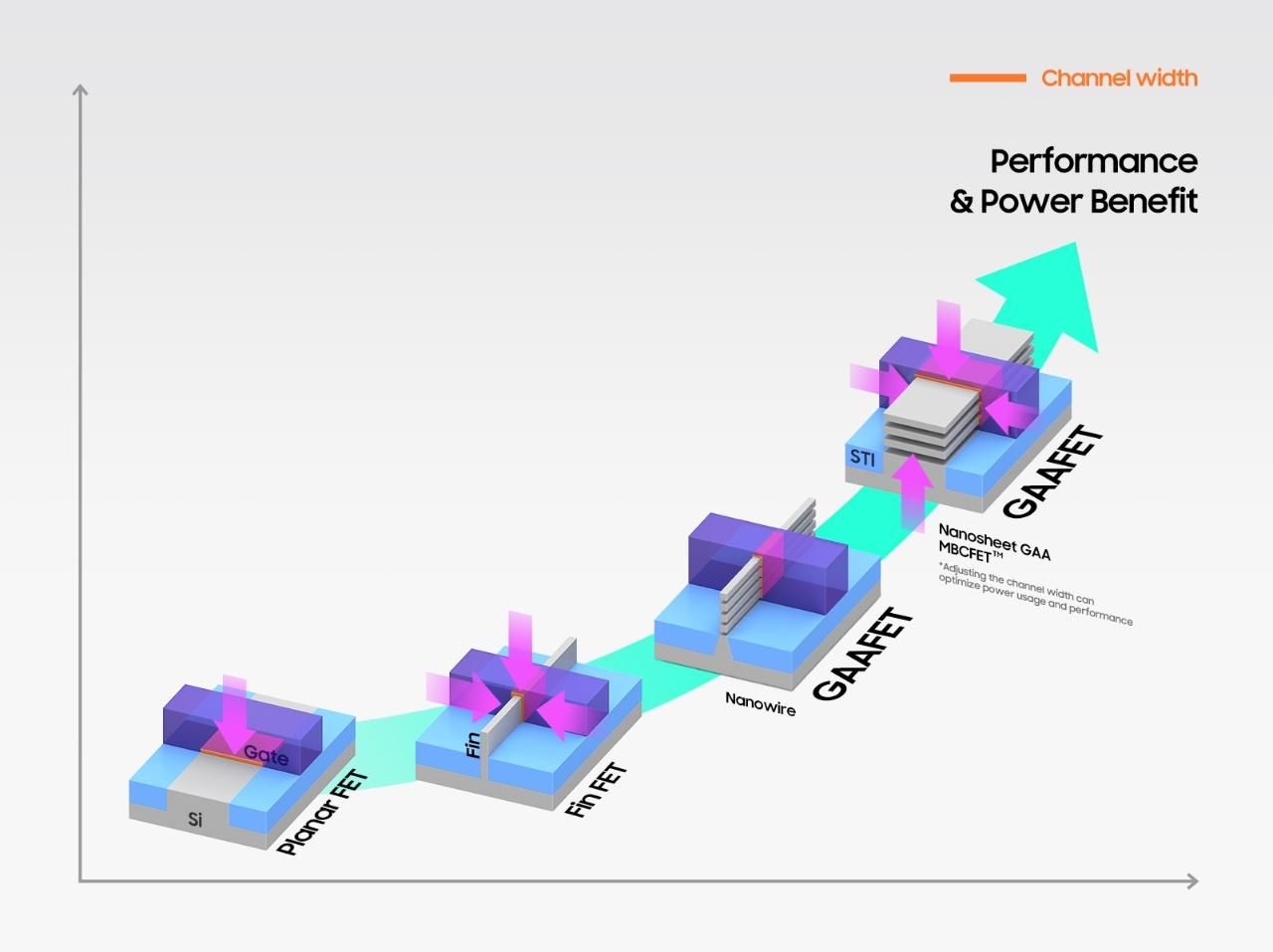

据悉,GAA(Gate-All-Around FET)是一种全能栅晶体管,被广泛认为是鳍结构的下一代继承者。它实现了栅极和沟道之间的四面包围,每一面都有接触,所以与沟道的接触面积更大,所以可以实现比FinFET更好的开关控制,解决大部分可能的漏电流,GAA的沟道控制能力更强,可以进一步小型化。

此外,GAA的设计灵活性非常有利于设计技术的协同优化,有助于实现更好的PPA优势。

目前主流的FinFET工艺(鳍式场效应晶体管)在工艺缩减到5nm后,基本达到了物理极限。鳍距太近,漏电重现,物理材料的限制,让3D FinFET晶体管难以为继。

可以说GAA工艺取代FinFET工艺是一个必然的过程。

因此,为了夺回“代工份额第一”的称号,三星在GAA工艺上下了大赌注,不仅率先投产,还声称三星的3nmGAA技术使用了宽沟道纳米片,可以提供比使用窄沟道纳米线的GAA技术更高的性能和能耗比。

在3nmGAA技术上,三星调整了纳米晶体管的沟道宽度,以优化功耗和性能。相比其5nm工艺,第一代3nmGAA工艺可降低功耗45%,提升性能23%,减少芯片面积16%。第二代3nmGAA技术功耗降低50%,性能提升30%,芯片面积减少35%。

但是想象很美好,现实却很残酷。看来GAA工艺面临的更复杂的问题也不是那么好解决的。宣布2022年量产3nmGAA的三星,直到今天也没能解决良品率问题,甚至在之前的报道中影响了自家Exynos 2500芯片的生产。

另一方面,其最大的竞争对手台积电仍然稳步改进其3nm节点的FinFET工艺,凭借良好的性能和成熟的工艺,不仅赢得了苹果的订单,也为其GAA工艺赢得了更多的时间。

据介绍,台积电在2nm工艺研发方面取得重大突破,将于2025年切入GAA技术并实现量产。

只能说留给三星的时间不多了。如果今年还不能提高3nmGAA的良率,错过高通和联发科的3nm芯片代工订单,那只能提前祈祷,凭借在GAA工艺上积累的经验,能在2nm节点与台积电决战。